# INSIGHT SIP DESIGN PROCESS

## SIMPLE PCB DESIGN

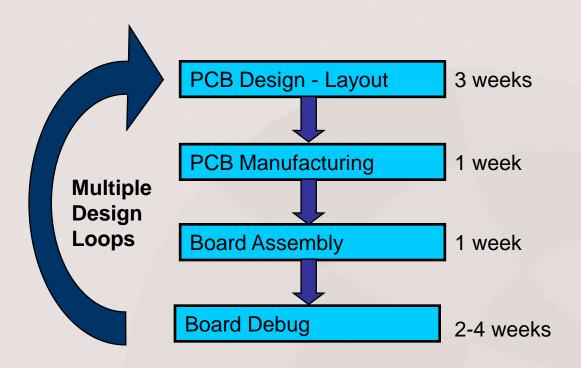

#### **Board Design**

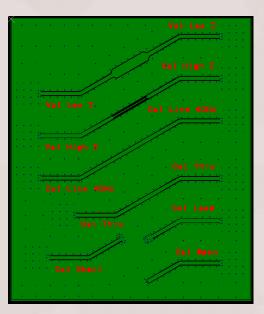

Typical Lead Time for 1 loop: 7-9 weeks

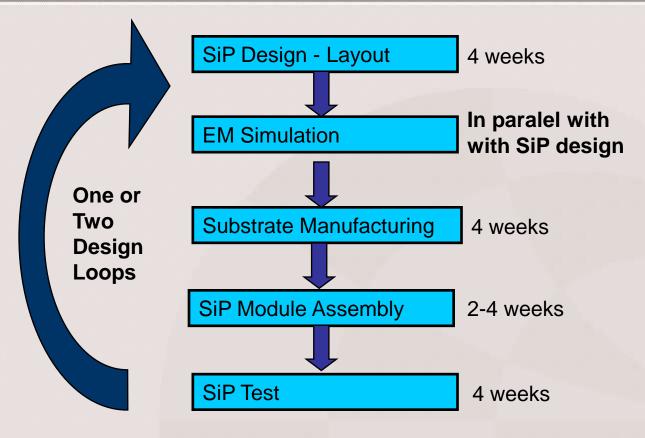

#### SIMPLE SIP DESIGN

#### SiP design

Typical Lead Time for 1 loop: 14-16 weeks

### More Complex Designs

Let's examine the situation when the design is more complex!!!

→ More than 2 die, More than 400 connections

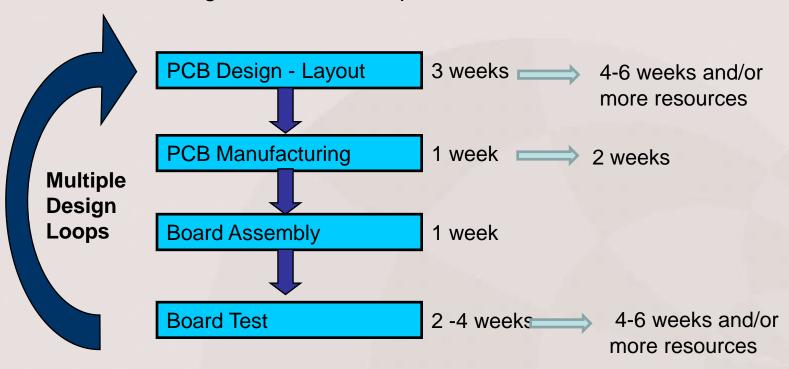

#### COMPLEX PCB DESIGN

More than 5 large LGA, BGA components, More than 500 nets

#### **Board Design**

Typical Lead Time for 1 loop: 11-15 weeks

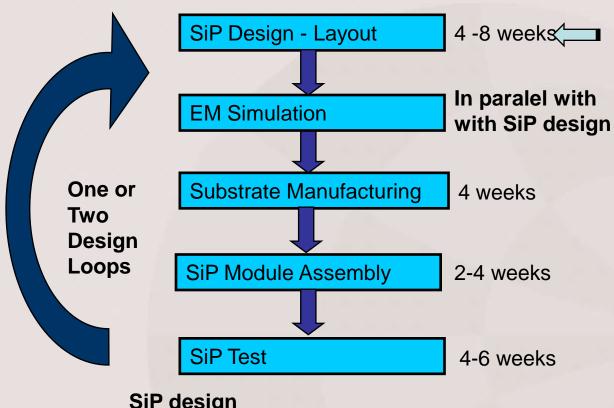

#### COMPLEX SIP DESIGN

More than 2 die more than 400 nets Complex RF interactions

SiP design

Typical Lead Time for 1 loop: 14-22 weeks

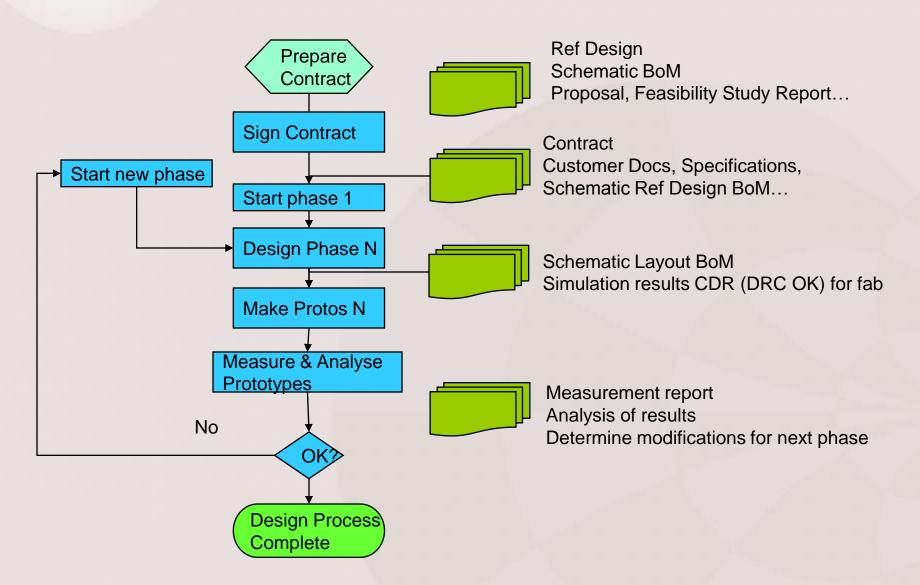

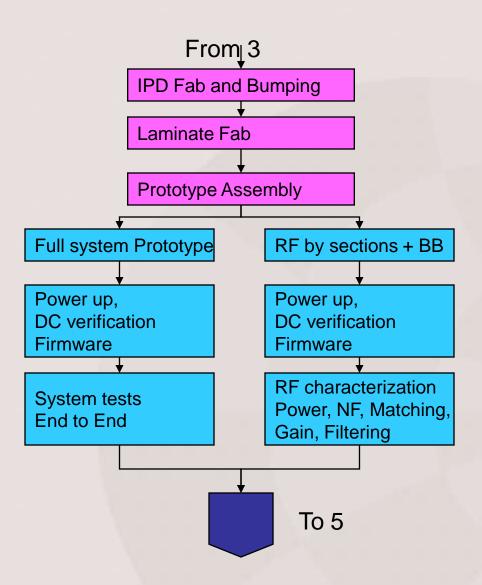

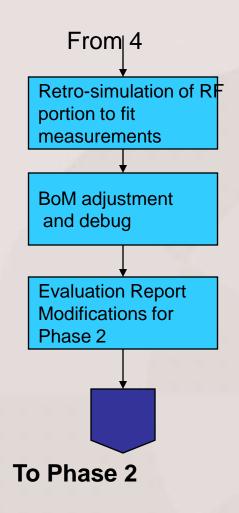

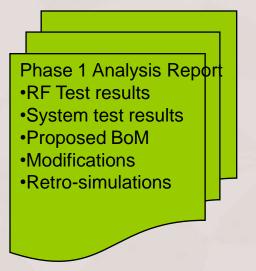

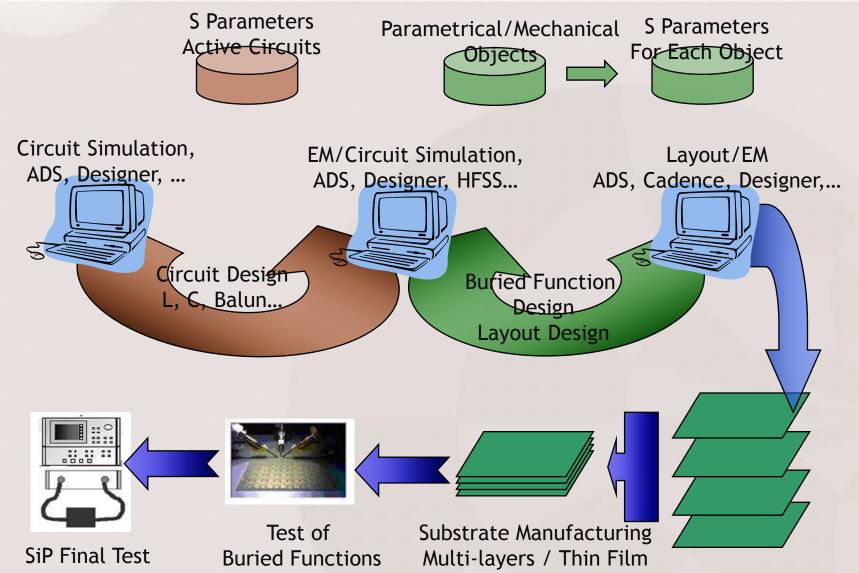

#### OVERALL DESIGN PROCESS

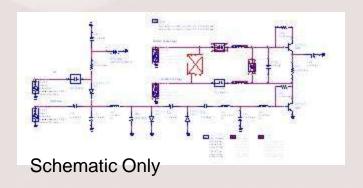

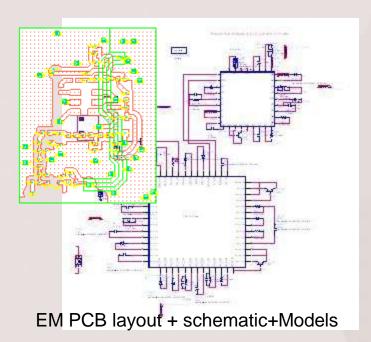

# SCHEMATIC AND EM LAYOUT

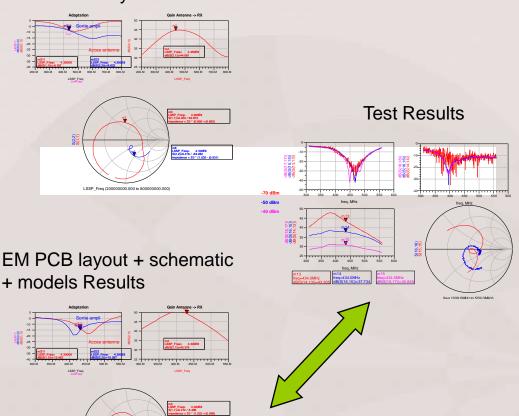

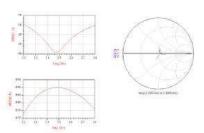

#### Schematic only Simulation Results

Adjust model complexity for fit

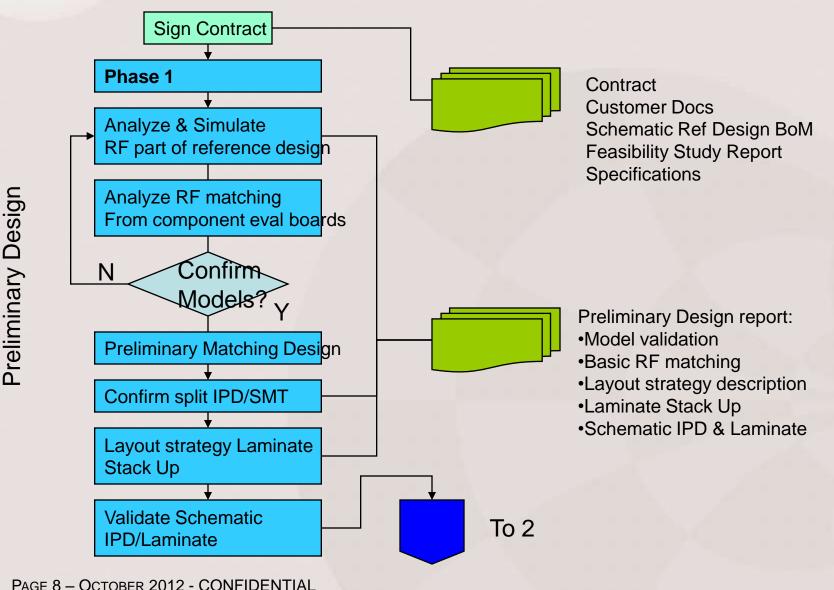

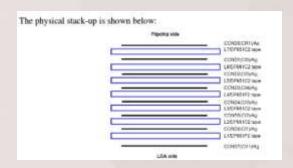

#### PRELIMINARY DESIGN

- RF matching

- IPD/SMT split

- Schematic with split

- BoM finalized

- Stack up finalized

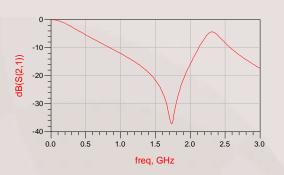

Simulation results for the balun alone for variant B (50/70 ohm) are shown below:

The balun has also been simulated with their matching circuit and components. In order to verify the bandwidth and sensitivity it has been assumed that the match is to 70 +/-j7.

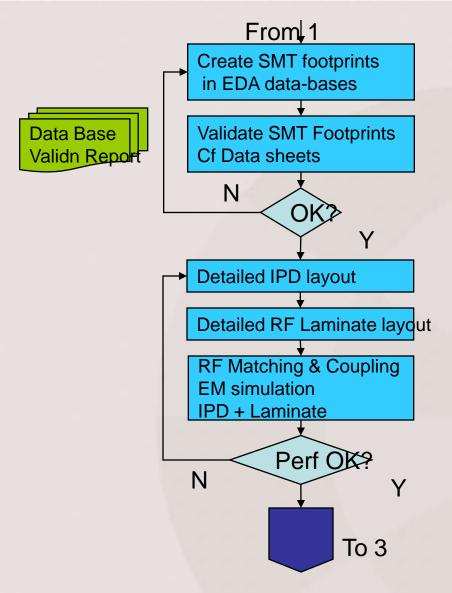

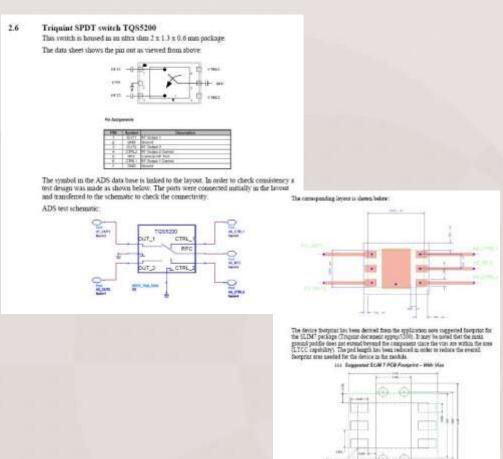

#### DATA BASE VALIDATION

- Compare SMT schematic, pinouts, layout,

- Supplier data

- ADS data base

- Allegro/mentor data base

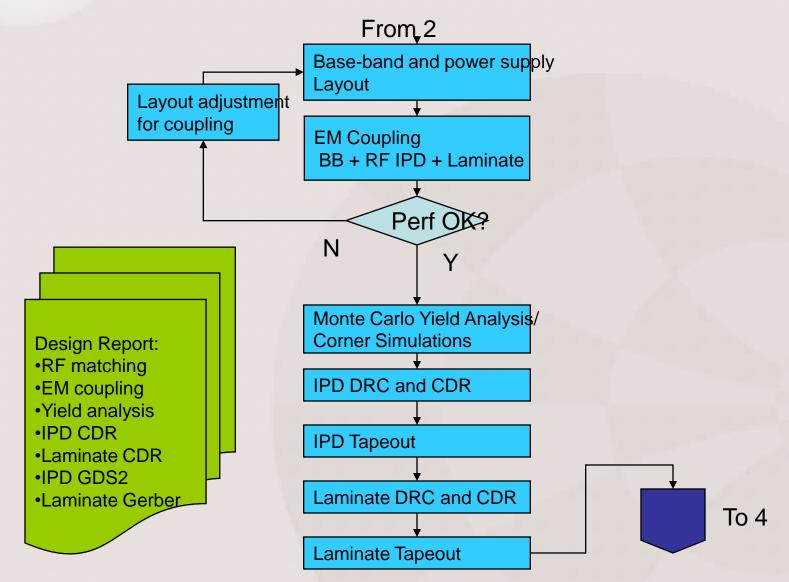

#### DETAIL DESIGN

RV1 VCC\_RF DECOUPLING C7

- RF Design of IPD/LTCC or other

- RF simulation of Laminate/LTCC

- Yield Analysis

- Layout of IPD/LTCC

- Layout of Laminate

- EM Coupling RF to BB and RF to DC

- GDSII and Gerber files

- Design Report

# DETAIL BURIED RF FUNCTIONS

#### TEST & DEBUG

- System test

- CMU200 or alternative (Project specific)

- RF testing

- RS ZVM

- SMIQ/AMIQ vector signal generators

- Cascade Probe station

- Spectrum/modulation

Analyser MXA with VSA

incorporated for 3G/GSM

# THANK YOU

# WWW.INSIGHTSIP.COM

#### To contact us:

mailto: rfipsales@insightsip.com

Tel: +33 (0) 607 771 474 / +33 (0) 678 559 519